2025 International Workshop on Advanced Interconnects Ningbo, China

**WAI 2025**

November 5 - 7, 2025

Advance program

#### ORGANIZERS AND TECHNICAL SPONSORS

## SPONSORSHIP ACKNOWLEDGEMENT

The Organizers of WAI 2025 gratefully acknowledge the following generous contributions:

## cādence

# cādence° Clarity 3D Solver 3D electromagnetic simulations delivering speed, accuracy, capacity, and streamlined workflows ▶ Run dozens of accurate simulations in the time legacy tools take to run one ▶ Solve large, more complex designs with cost-effective computers ▶ Accelerate project schedules with an optimized design and analysis flow

## cādence°

## Accelerate Design Schedules with Accurate System-Level SI/PI Analysis

Deliver 10X design productivity with Cadence PCB and IC package analysis tools

- Proven in-design interconnect modeling

- In-design PDN analysis for PCB and IC packaging

- ► Comprehensive, end-to-end SI/PI analysis tools

- Deliver products on time and within budget

Accurate design and analysis flows identify issues early and ensure products meet cost, performance, and reliability goals.

#### www.cadence.com/go/SigrityX

## Dloorplf 昆山德普福电子科技有限公司

## ▶ 关于我们

德普福是一家以研发为主导的科技型企业,提供完整的射频微波信号连接及行业解决方案,创新和品质是德普福公司的核心竞争力。产品种类丰富,涵盖晶圆测试探针、RF Socket、射频同轴连接器、转接器、多通道射频连接器、射频电缆组件,以及射频开关矩阵系统,广泛应用于半导体、光通信和毫米波测试测量等领域。

RF Switch DC-110GHz

网址: www.dloorplf.com 德普福.com

联系电话: 13812951881

地址: 江苏省昆山市玉山镇玉杨路1001号3幢

## LinkE须翌科技

珠海领翌科技有限公司专注于高速连接器组件产品,致力于通过理论和工程创新为行业带来更具竞争力的解决方案。

基于自主研发的DirectPin技术, 领翌科技的高密度内部互联产品能够应用在PCle Gen6/7、224G/448G PAM4等场景, 具备优异的SI性能。

PCIe Gen6/7 连接器线缆组件 (兼容SFF-TA-1016 Footprint)

高速高密度连接器组件 (支持224G/448G应用)

## 联系我们

bd@linketech.cn

152 - 1114 - 3254

🙎 : 珠海市香洲区科健路66号正菱高科园1栋1层

(\$): www.linketech.cn

### TABLE OF CONTENTS

| INVITATION FROM THE GENERAL CHAIR             | 9  |

|-----------------------------------------------|----|

| CHAIRS FOR TECHNICAL PROGRAM COMMITTEE        | 10 |

| ORGANIZING COMMITTEE                          | 11 |

| TECHNICAL PROGRAM COMMITTEES                  | 12 |

| GENERAL INFORMATION                           | 13 |

| REGISTRATION                                  | 13 |

| KEYNOTE SPEECHES I                            | 21 |

| KEYNOTE SPEECHES II                           | 22 |

| KEYNOTE SPEECHES III                          | 23 |

| KEYNOTE SPEECHES IV                           | 24 |

| KEYNOTE SPEECHES V                            | 25 |

| INDUSTRY PLENARY I                            | 26 |

| INDUSTRY PLENARYII                            | 26 |

| INDUSTRY PLENARY III                          | 27 |

| INDUSTRY PLENARY IV                           | 27 |

| INDUSTRY PLENARY V                            | 28 |

| INDUSTRY PLENARY VI                           | 28 |

| INDUSTRY PLENARY TALK I                       | 29 |

| INDUSTRY PLENARY TALKII                       | 29 |

| PANEL DISCUSSION I                            | 33 |

| PANEL DISCUSSION II                           | 35 |

| PANEL DISCUSSION III                          | 37 |

| PANEL DISCUSSION IV                           | 39 |

| HOW TO GET TO THE HUALUXE® Ningbo Harbor City | 41 |

| ACCOMMODATION                                 | 42 |

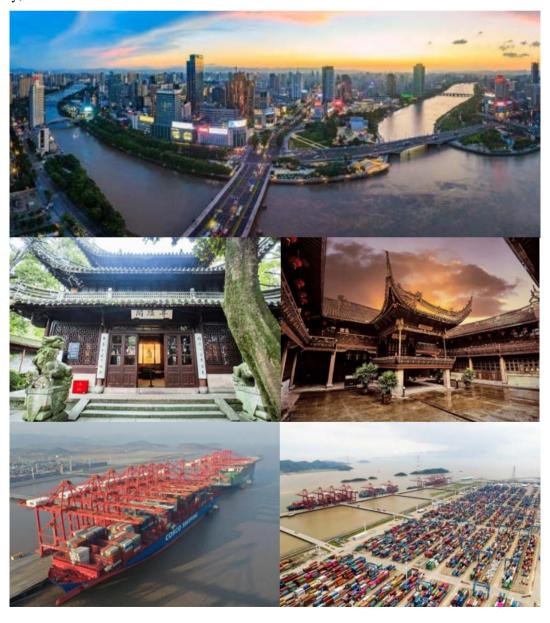

| ABOUT NINGBO                                  | 44 |

#### INVITATION FROM THE GENERAL CHAIR

Dear Colleagues and Friends,

Welcome to WAI 2025! This is the second International Work shop on advanced interconnects. The scope of this workshop includes, but is not limited to signal integrity and power integrity of an electronic system and its components including advanced interconnects, integrated circuits, IC packages, printed circuit boards, cables, connectors, as well as other relevant electronic and microelectronic components, and signal integrity/ power integrity co-design.

WAI 2025 also welcomes all papers or presentations related but not limited to electromagnetic environments; interference control; EMC and EMI modeling; high power electromagnetics; EMC standards, methods of EMC measurements; computational electromagnetics and signal and power integrity, as applied or directly related to EMC problems; transmission lines; electrostatic discharge and lightning effects; EMC in wireless and optical technologies; EMC in printed circuit board and system design; radio-frequency interference problems; artificial intelligence-assisted EMC/SI/PI design methodologies.

We would like to express our thanks to our coorganizers, sponsors, contributors and all of the attendees for your hard work and effort! Our best wishes are to all WAI 2025 attendees, and we hope all of you enjoy your time in Ningo and have a great time!

#### WAI 2025 General Chairs

Jun Fan, IEEE Fellow Qiushi Professor, Zhejiang University

Er-Ping Li, IEEE Fellow

Qiushi Chair Professor, Zhejiang University

#### CHAIRS FOR TECHNICAL PROGRAM COMMITTEE

Xiaoning Ye, IEEE Fellow

Intel

Bo Pu

DeTooLIC Technology

Ling Zhang

Zhejiang University

#### **ORGANIZING COMMITTEE**

#### **Organizing Committee Chair**

#### **Special Sessions Chair**

Hanzhi Ma, Zhejiang University, China

Francesco de Paulis, University of L'Aquila, Italy

#### **Award Chair**

Xiaoning Ye, Intel, USA

#### **Publication Chair**

Siping Gao, Nanjing University of Aeronautics and Astronautics, China

#### **Symposium Secretary**

Yidan Hu, DeTooLIC Technology, China Jing Yang, DeTooLIC Technology, China Jiwei Li, DeTooLIC Technology, China Haiqing Zhang, DeTooLIC Technology, China

#### TECHNICAL PROGRAM COMMITTEES

The TPC are led by the TPC Chairs including **Dr. Xiaoning Ye**, **Dr. Bo Pu**, and **Prof. Ling Zhang**. The Technical Committee members for the 2025 WAI are listed as below (sorted by last name).

Seungyoung Ahn KAIST. Korea **Daryl Beetner**Missouri University of Science and Technology, USA

**Alexandre Boyer** LAAS-CNRS, France

Qiangming Cai Southwest University of Science and Technology, China **Ji Chen** University of Houston, USA Wenchao Chen Zhejiang University, China

Xiaohe Chen

China University of Petroleum, Beijing, China **Xiong Chen** Xi'an Jiaotong University, China Xiuqin Chu Xidian University, China

Zhufei Chu

Ningbo University, China

**Bernd Deutschmann**

Graz University of Technology, Zhejian Austria

**Shurong Dong**

Zhejiang University, China

Richard Gao

A\*STAR, Singapore

Siping Gao

Nanjing University of Aeronautics and Astronautics, China

Shiquan He

University of Electronic Science and Technology of China, China

**Chulsoon Hwang**

Missouri University of Science and Technology, USA

Lijun Jiang

Missouri University of Science and Technology, USA

Da Li

Zhejiang University, China

Tianwu Li

Zhejiang University, China

Shufang Li

Beijing University of Posts and Telecommunications, China

Yan Li

China Jiliang University, China

Enxiao Liu

A\*STAR, Singapore

Hanzhi Ma

Zhejiang University, China

**David Pommerenke**

Graz University of Technology, Austria

Francesco de Paulis

University of L'Aquila, Italy

Qiang Ren

Beihang University, China

Dan Shi

Beijing University of Posts and Telecommunications, China

Xinglin Sun

Zhejiang University, China

Yin Sun

DeTooLIC Technology, China

Shurun Tan

Zhejiang University, China

Fayu Wan

Nanjing University of Information Science and Technology, China Yansheng Wang Rivos Inc., USA **Hanfeng Wang**Google Inc., USA

Jian Wang

Ningbo University, China

Xing-Chang Wei

Zhejiang University, China

**Zhiping Yang** PCB Automation Inc., USA

Da Yi

Chongqing University, China

**Huapeng Zhao**

University of Electronic Science and Technology of China, China

Wensheng Zhao

Hangzhou Dianzi University, China

Zhaofu Zhang

Wuhan University, China

Yuyu Zhu

Southwest University of Science and Technology, China

Cheng Zhuo

Zhejiang University, China

Jiang Xiao,

Keysight Technologies (China) Co., Ltd, China

#### **GENERAL INFORMATION**

#### REGISTRATION

#### **Registration link:**

please register an account at <a href="http://www.wai-emc.com/wai2025/registration">http://www.wai-emc.com/wai2025/registration</a>.

Each participant or each presenting author must pay a non-refundable pre-registration fee. Only pre-registered and paid submissions before 26 October, 2025 will be scheduled in the symposium program. Inclusion of the submissions in the final Technical Program (one-page abstracts only), and WAI Proceedings (one-page abstracts only) is guaranteed only after the pre-registration of the presenting author is completed.

Your pre-registration will be valid only provided the payment is received timely. The pre-registration deadline is 26 October, 2025. The on-site registration opportunity is for non-presenting authors only. The registration fee for your articles is non-refundable. The registration fee is the same for presenting authors and non-presenting authors.

| Onsite Participants       | Registration Fee   |

|---------------------------|--------------------|

| Student Full Price Ticket | RMB 1480 (USD 208) |

| Regular Full Price Ticket | RMB 2480 (USD 348) |

#### **CONFERENCE VENUE**

#### **HUALUXE® Ningbo Harbor City**

The HUALUXE Hotel in Ningbo Port City is a new high-end five-star hotel brand under the InterContinental Hotels Group. Based on a globally renowned excellent management system, it is committed to providing you with a space that is close to nature and luxurious, bringing a new definition of Chinese hospitality to the Chinese people with "courtesy, respect, harmony, and expressiveness".

It is your ideal choice for business socializing and gathering with family and friends. The Huayi Hotel in Ningbo Port City understands the business and social needs of Chinese people. From relaxed meetings at the "Jumingyi" tea house, private banquets at the "Jushanyi" VIP world, to leisure and wellness at the Huayi Health Club, a series of public and private spaces fully meet the various business, social, and leisure entertainment needs of guests.

#### LOCATION MAP AROUND THE CONFERENCE VENUE

★ HUALUXE® Ningbo Harbor City

Address: No. 1199 Changjiang Road, Beilun District, Ningbo City, Zhejiang Province (+86 574 86799999)

$Website: \underline{https://www.ihg.com.cn/hualuxe/hotels/cn/zh/ningbo/ngbul/hoteldetail\#}$

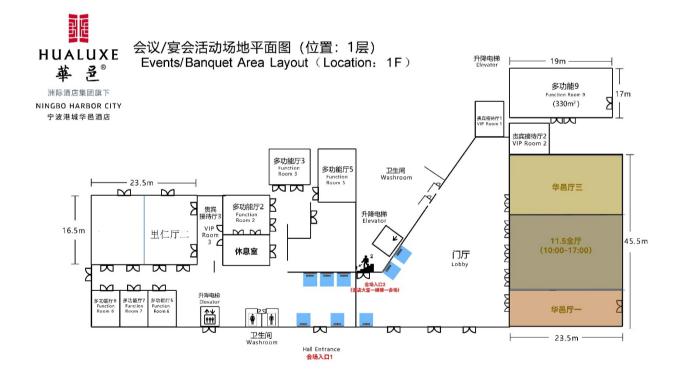

#### REGISTRATION HOURS/FLOOR PLAN

Admission to all sessions and hosted functions requires the attendance identification. Please wear your name badge at all times.

#### **Registration time**

☐ November 4, Tuesday 14:00 - 19:00

$\square$  November 5, Wednesday 7:30 – 9:00

#### **Registration Address**

#### **HUALUXE® Ningbo Harbor City**

宁波港城华邑酒店

No. 1199 Changjiang Road, Beilun District, Ningbo City, Zhejiang Province

#### **EXHIBITION HALL AND MEETING ROOMS**

#### Opening Ceremony (开幕式及大会讲座)

HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

#### Parallel Sessions (分会场)

Room 1: HUALUXE Hall 1 @Level 1 (1 楼华邑厅一)

Room 2: HUALUXE Hall 3 @Level 1 (1 楼华邑厅三)

Room 3: Liren Hall 2 @Level 1 (1 楼里仁厅二)

#### PROGRAM OVERVIEW

Symposium Web: <a href="http://www.wai-emc.com/wai2025/">http://www.wai-emc.com/wai2025/</a>

| Symposium Hours                         |  |  |  |

|-----------------------------------------|--|--|--|

| November 5, 2025, 8:30 – 17:30          |  |  |  |

| November 6, 2025, 8:40 – 17:40          |  |  |  |

| November 7, 2025, 8:40 – 11:40          |  |  |  |

| November 5 – Wednesday                  |  |  |  |

| ☐ Official Opening and Keynote Speeches |  |  |  |

| ☐ Industry Plenary                      |  |  |  |

| ☐ Technical Exhibition                  |  |  |  |

| November 6 – Thursday                   |  |  |  |

| ☐ Oral Presentation                     |  |  |  |

| ☐ Young Professional Session            |  |  |  |

| ☐ Technical Exhibition                  |  |  |  |

| ☐ Banquet Dinner                        |  |  |  |

| November 7 – Friday                     |  |  |  |

| ☐ IBIS Summit                           |  |  |  |

| ☐ Oral Presentation                     |  |  |  |

| ☐ Technical Exhibition                  |  |  |  |

## **2025** International Workshop on Advanced Interconnects

November 5-7, 2025

| Date     | Time        | Agenda           |

|----------|-------------|------------------|

|          | 08:30-08:40 | Opening Ceremony |

|          | 08:40-12:20 | Keynote Speeches |

|          | 12:20-14:00 | Lunch            |

| Nov. 5th | 14:00-15:30 | Industry Plenary |

|          | 15:30-15:50 | Tea Break        |

|          | 15:50-17:20 | Industry Plenary |

|          | 17:30       | Dinner (Buffet)  |

## 2025 International Workshop on Advanced Interconnects November 5-7, 2025

| Date     | Time        | HUALUXE Hall 1(华邑厅一)                                                         | HUALUXE Hall 3(华邑厅三)                                                     | Liren Hall 2 (里仁厅二)                                                                                                    |

|----------|-------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|          | 8:40-10:00  | [SS1] Signal and Power Integrity for High-Speed Interconnect Design          | [ SS3] Advance in Electromagnetism Simulation and Analysis Method        | Industry Plenary Talk (I-II)                                                                                           |

|          | 10:00-10:20 |                                                                              |                                                                          |                                                                                                                        |

|          | 10:20-11:00 | [SS1] Signal and Power Integrity for High-Speed<br>Interconnect Design       | [ SS3] Advance in Electromagnetism Simulation and Analysis Method        | Panel Discussion I                                                                                                     |

|          | 11:00-12:00 | [SS1] Signal and Power Integrity for High-Speed Interconnect Design          | [ SS3] Advance in Electromagnetism Simulation and Analysis Method        | Addressing the Ever-Growing Challenges in High-Speed Interconnect Designs in the AI Era: EDA Perspectives              |

|          | 12:00-13:20 | Lunch                                                                        | a & Rest                                                                 | Young Professional Session (providing lunch)                                                                           |

|          |             | HUALUXE Hall 1(华邑厅一)                                                         | HUALUXE Hall 3(华邑厅三)                                                     | Liren Hall 2(里仁厅二)                                                                                                     |

| Nov. 6th | 13:20-14:00 | [SS2] Recent Advances in EMI/EMC Techniques                                  | [SS5] Machine Learning Based EMC/SI/PI Design                            | Panel Discussion II<br>Data Center High-Speed Interconnect in the AI Era:                                              |

|          | 14:00-14:40 | [SS2] Recent Advances in EMI/EMC Techniques                                  | [SS5] Machine Learning Based EMC/SI/PI Design                            | Part I - Innovations in Materials and Manufacturing  Panel Discussion III                                              |

| -        | 14:40-15:20 | [SS2] Recent Advances in EMI/EMC Techniques                                  | [SS5] Machine Learning Based EMC/SI/PI Design                            | Data Center High-Speed Interconnect in the AI Era: Part II - Architecturing the Interconnect for the Future            |

|          | 15:20-15:40 |                                                                              | Tea Break                                                                |                                                                                                                        |

|          | 15:40-16:40 | [SS4] Power Integrity Design Techniques                                      | [SS6] Antenna and Metasurface Design Techniques                          | Panel Discussion IV<br>Trends in Smart Devices and Challenges Related to<br>Electromagnetic Interference in the AI Era |

|          | 16:40-17:40 | [SS4] Power Integrity Design Techniques                                      | [SS6] Antenna and Metasurface Design Techniques                          |                                                                                                                        |

|          | 18:30       |                                                                              | Banquet Dinner                                                           |                                                                                                                        |

|          | Time        | HUALUXE Hall 1(华邑厅一)                                                         | HUALUXE Hall 3(华邑厅三)                                                     | Liren Hall 2 (里仁厅二)                                                                                                    |

|          | 8:40-9:40   | [SS7] Electromagnetic Compatibility of Integrated Circuits and Components    | [SS8] Advanced Signal Integrity Modeling, Design, and Testing Techniques | IBIS Summit                                                                                                            |

| Nov. 7th | 9:40-10:00  | Tea Break                                                                    |                                                                          |                                                                                                                        |

|          | 10:00-11:40 | [SS7] Electromagnetic Compatibility of Integrated<br>Circuits and Components | [SS8] Advanced Signal Integrity Modeling, Design, and Testing Techniques | IBIS Summit                                                                                                            |

| Ĭ        |             |                                                                              | END                                                                      |                                                                                                                        |

#### **KEYNOTE SPEECHES I**

**TITLE High-Speed Interconnect in Data Centers TIME**8:40 – 9:20, November 5th

**VENUE** HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

**SPEAKER** Xiaoning Ye

#### **ABSTRACT**

The data center is undergoing a profound shift from CPU-centric design to accelerated computing and generative-AI-centric architectures. The fundamental unit of compute is no longer a single server but a distributed system at rack and cluster scale. Achieving performance now hinges on massive data parallelism—and the interconnect has become the first-order constraint as system scale and bandwidth rise.

This speech traces the evolution of high-speed interconnects in modern data centers and explains why signal integrity now drives the ecosystem. We will also show how hardware-architecture innovations can relieve interconnect bottlenecks and unlock scalable performance.

#### **BIOGRAPHY**

Dr. Xiaoning Ye is currently a Senior Principal Engineer at Data Center Group of Intel Corporation, specialized in high-speed interconnects. He received his Bachelor's and Master's degrees in electronics engineering from Tsinghua University, Beijing, China, in 1995 and 1997 respectively, and Ph.D. degree in electrical engineering from Missouri University of Science and Technology in 2000.

Dr. Ye published over 100 technical papers in IEEE and other technical journals and conferences, with over 3600 citations. He holds 20 patents and a few more applications in the areas of high-speed signaling. He also led the development of two industry standards on interconnect characterization: IEEE 370, and IPC test method 2.5.5.14. Dr. Ye is currently serving as Vice President of Technical Services for IEEE EMC Society. He was Chair of the IEEE EMC Society Technical Advisory Committee from 2017 to 2020, and has been an Associate Editor of IEEE Transactions on Electromagnetic Compatibility since 2016. Dr. Ye received Technical achievement award of IEEE EMC Society in 2015, and was elevated to IEEE fellow in 2021.

#### **KEYNOTE SPEECHES II**

TITLE Accelerating Innovation: AI-Driven Advances in Sigrity, Clarity, and Optimality

**TIME** 9:20 – 10:00, November 5th

**VENUE** HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

**SPEAKER** Qin Liu

#### **ABSTRACT**

With the electronic systems being more complex, efficiency and accuracy requirement on design and simulation is becoming more and more demanding. At Cadence, we're meeting this challenge head-on by bringing AI and automation to every stage of design. Sigrity-APX, as an intelligent advanced IC Package Extractor, embeds machine learning model in many typical but challenging structures, such as vias, degassing hole planes, and traces with degassing hole planes. Clarity-PI is also launched as an AI accelerated Clarity extraction tool with

faster, smarter and more stable solution, benefitting IC, interposer, and packaging extraction applications. Also, with new statistical functions and AI surrogate models, our advanced optimization engine allows user to explore the design space with higher efficiency. Furthermore, major break through is made in using generative AI beyond traditional optimization, we can now automate the entire workflow inside the design platform by creating new design from scratch, identifying critical regions, auto-cutting and extracting, and running targeted optimizations. AI algorithm, learning from Cadence's massive simulation datasets, predicts electromagnetic effects with high fidelity. This means fewer manual tweaks and more reliable results, accelerating the path to signoff.

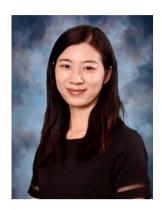

#### **BIOGRAPHY**

Qin Liu is a Software Engineering Director in Sigrity R&D US Group at Cadence Design Systems, mainly focused on Clarity 3D full-wave electromagnetic software development. Dr. Liu has over 14 years' experience in developing advanced electromagnetic analysis and simulation methods. She received the B.Eng. degree in electronic engineering from the University of Science and Technology of China, Hefei, China, in 2011, and the Ph.D. degree in electrical and electronic engineering from The University of Hong Kong, Hong Kong, in 2015. From 2015 to 2018, she is a Post-Doctoral Fellow with The University of Hong Kong and a Postdoctoral Research Associate with the University of Illinois at Urbana Champaign. Since 2018, she has been working for Sigrity/Clarity R&D Group at Cadence Design System, San Jose, USA.

#### KEYNOTE SPEECHES III

| TITLE | <b>High-Speed Interconnects in Semiconductor Systems: Where Physics Meets</b> |  |

|-------|-------------------------------------------------------------------------------|--|

|       | Performance                                                                   |  |

|       |                                                                               |  |

**TIME** 10:20 – 11:00, November 5th

**VENUE** HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

**SPEAKER** En-xiao Liu

#### **ABSTRACT**

As semiconductor scaling is knocking on the door of the physical limits, interconnects open a new window into the spotlight of realizing system speed, bandwidth, energy, and reliability.

In this dense and deep connection era, multi-GHz signalling amplifies loss, crosstalk, and electrical and electromagnetic as well as multiphysics interactions across chip, package, and board hierarchies. Signal integrity, power integrity, and

electromagnetic compatibility (SI/PI/EMC) can only be better achieved through multi-parameter and multi-objective early co-design and co-optimisation.

On one hand, advanced packaging, chiplets, and co-packaged optics create dense, multi-modal channels offering new hopes and new promises. On the other hand, AI and Machine learning (ML) are demanding even more from high-speed interconnects.

Can we leverage new physics, novel materials, heterogeneous architectures, AI/ML, and so on, to transform interconnects from passive links into active enablers of ultra-wide bandwidth, high-speed, energy-efficient, and robust systems?

#### **BIOGRAPHY**

En-Xiao Liu is currently Senior Principal Scientist and Deputy Department Director at A\*STAR Institute of High Performance Computing. He is also an adjunct Associate Professor at the National University of Singapore. His research interests are in the areas of computational electromagnetics, high-speed electronics and packaging, electromagnetic compatibility (EMC), and AI/ML applications.

Dr. Liu received the team award of Singapore President's Technology Award (2019), ASEAN and IES Prestigious Engineering Achievement Award (2019), and the IEEE EMC Society Technical Achievement Award (2016). He was an IEEE EMC Society Distinguished Lecturer, the past Chair of the IEEE EMC Singapore Chapter, and TPC/General Chair for several international conferences. He is an Associate Editor of four IEEE journals (T-EMC, T-SPI, L-EMCPA, and T-CPMT). He co-edited the T-EMC (a) Special Section on Nature-Inspired Algorithms for EMC/SI/PI (2018) and (b) the Special Issue on AI/ML & Deep Learning for EMC (2024). He was a plenary speaker at the EMC Japan/APEMC Okinawa 2024 Symposium.

#### **KEYNOTE SPEECHES IV**

TITLE New Opportunity, New Journey

TIME 11:00 – 11:40, November 5th

**VENUE** HUALUXE Hall @Level 1(1 楼华邑宴会厅)

**SPEAKER** Stanley Zheng

#### **ABSTRACT**

With the rapid development of digitization, intelligence, and the great prospect of semiconductor industry, we are standing at an unprecedented node in the window where there are constrains of supply chain and technology bifurcations, this presents both new opportunities and unprecedented challenges, requiring industry and academia to jointly explore technological breakthrough with STCO Collaborative Development

#### **BIOGRAPHY**

Stanley Zheng graduated from the Department of Computer Science at Fudan University and holds an MBA from Macau University of Science and

Technology. He has served as Senior Engineer at Inventec, Engineering Manager at Phoenix Technologies, Technical Support Manager/Strategy Director at Intel, and Director of Semiconductor Industry Development at Huawei. His work experience spans OS development, BIOS/EFI development, chip technical support, marketing, ecosystem promotion, IP strategy, 7nm chip product development, and industry development. He is the only person in Intel China ever served as a global chip leader. He currently serves as the Director of External Cooperation Committee and Chief of Standards at EDA<sup>2</sup>.

#### **KEYNOTE SPEECHES V**

TITLE Multiphysics EDA: Advanced Computing beyond Simulation

**TIME** 11:40 – 12:20, November 5th

**VENUE** HUALUXE Hall @Level 1(1 楼华邑宴会厅)

**SPEAKER** Qiwei Zhan

#### **ABSTRACT**

When discussing multiphysics modeling, the finite element method is one of the most widely used algorithms. However, especially for complex systems, there remains a significant gap between real-world requirements and current simulation capabilities. This challenge arises mainly due to extreme problem scales, unavoidable uncertainties, and prolonged simulation times.

Moreover, with IC design having entered the post-Moore's Law era, 3D chip integration has emerged as one of the most promising technologies. Yet, an effective

EDA tool that incorporates coupled electromagnetic, thermodynamic, and fluid effects is still lacking. These challenges motivate us to develop multiphysics EDA software, by integrating recent advances in computational methods and going beyond conventional FEM simulation. To be more specific, this talk will present interdisciplinary efforts, toward the systematic integration of CAD (mesh generation), CAE (unified discontinuous Galerkin methods), and CAM (data learning), empowered by the high-performance computing technology.

#### **BIOGRAPHY**

Qiwei Zhan received the B.S. degree in geophysics from the University of Science and Technology of China, Hefei, China, in 2013, and the M.S. degree in civil and environmental engineering (minor) and the Ph.D. degree in electrical and computer engineering from Duke University, Durham, NC, USA, in 2016 and 2019, respectively. From June 2019 to August 2020, he was a Peter O'Donnell Jr. Postdoctoral Fellow with the Oden Institute for Computational Engineering and Sciences, The University of Texas at Austin, Austin, TX, USA. Since September 2020, he has been a Tenure-Track Professor and a Ph.D. Supervisor with the College of Information Science and Electronic Engineering, Zhejiang University, Hangzhou, China. His research interests include multiphysics modeling, high-performance computing, uncertainty quantification, inverse problems, and scientific machine learning.

#### INDUSTRY PLENARY I

TITLE China's RISC-V High-Performance Computing: Exploration from Self-

**Developed IP to Ecosystem Construction**

**TIME** 14:00 – 14:30, November 5th

**VENUE** HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

**SPEAKER** Qingyuan Ren

#### **ABSTRACT**

This speech examines RISC-V's disruptive role in high-performance computing (HPC), highlighting global momentum and China's accelerated progress through strategic policy support. One of this evolution is RiVAI Technologies' Lingyu Processor—featuring a dual-core architecture, self-developed Core & NoC IP, and enterprise-grade RAS for data-center reliability. The speech further demonstrates a full-stack RISC-V HPC solution encompassing hardware co-developed with top OEMs and domestic software partners. Empowered by a robust ecosystem, RISC-V is advancing scenario-specific deployments (AI inference, industrial HPC) toward a multi-billion-dollar market, redefining next-generation computing infrastructure.

#### **BIOGRAPHY**

Mr. Ren Qingyuan graduated from Duke University and the University of Washington in the United States and previously held positions at leading industry companies such as Lenovo. In 2023, he joined RiVAI Technologies as Business Vice President, where he oversees the company's commercial and marketing operations.

#### INDUSTRY PLENARY II

| TITLE   | Testing Solutions for Ultra-High-Speed Products Signal Integrity Testing |  |

|---------|--------------------------------------------------------------------------|--|

|         | for Passive Components                                                   |  |

| TIME    | 14:30 – 15:00, November 5th                                              |  |

| VENUE   | HUALUXE Hall @Level 1(1 楼华邑宴会厅)                                          |  |

| SPEAKER | Xiangyang Ma                                                             |  |

#### **ABSTRACT**

With the advent of generative AI, artificial intelligence has achieved leapfrog development in the 2020s, placing higher demands on hardware in terms of computing power, storage, and data transmission—requiring faster iteration, higher speeds, and quicker responses. In an increasingly demanding market, how can we grasp the right direction and solutions for product R&D and manufacturing to create better products? Share Dloorplf's solutions.

#### **BIOGRAPHY**

Industry-leading expert developers: Proficient in high-frequency and millimeterwave communications, with 24 years of industry experience. Expertise in network

analysis, S-parameters, DCA, RF SI, and related systems and development technologies.

- •Possesses extensive project development management experience, having led full-cycle development and team management for 10G/40G Ethernet, 100G SR4/LR4, wireless modules, Apple millimeter-wave matrix, and 400G/800G optical transmission test systems. Expertise spans optical transmission, high-frequency transmission and integrity, and wireless signal system processing.

- •Proficient in both software and hardware: Expertise in C/VB language interface systems, mastery of high-frequency PCB design and signal processing.

#### **INDUSTRY PLENARY III**

**TITLE Development Status of InP and CMOS Heterogeneous Integration Technology TIME**15:00 – 15:30, November 6th

**VENUE** HUALUXE Hall @Level 1 (1 楼华邑宴会厅)

**SPEAKER** Rong Chen

#### ABSTRACT:

InP and CMOS are two distinct semiconductor materials with its unique advantages and limitations. InP materials feature high electron mobility and high cutoff frequency, making them suitable for high-frequency and optoelectronic device fabrication. CMOS materials offer high electron mobility and high integration density, making them ideal for digital integrated circuits. To achieve frequencies of >100 GHz, the heterogeneous integration of InP and CMOS can offer superior performance and application value. However, there are several technical challenges in the integration process: particularly concerning material compatibility, device interoperability, and manufacturing processes. As a result, the heterogeneous integration of InP and CMOS has become a key area of research

in recent years. This paper analyzes the development status of InP and CMOS heterogeneous integration technology, examines the main challenges currently faced by the technology, and explores future development directions, providing strong support for high-frequency (>100 GHz) wireless communications, radar imaging, and other high-performance applications.

#### **BIOGRAPHY**

Rong chen is an advanced packaging expert at CETC Chip Institute and Head of the Microsystem Integration Group at the National Laboratory of Integrated Circuits and Microsystems. She has led or participated in over ten national and ministerial-level key projects. Her current research is dedicated to 2.5D packaging and Chiplet technologies for high-speed, high-precision mixed-signal circuits, with over 10 publications and 3 patents.

#### INDUSTRY PLENARY IV

| TITLE   | Research on Simulation and Testing of Signal Integrity and Power Integrity |

|---------|----------------------------------------------------------------------------|

| TIME    | 15:50 – 16:20, November 5th                                                |

| VENUE   | HUALUXE Hall @Level 1(1 楼华邑宴会厅)                                            |

| CDEAZED | T' 71                                                                      |

#### **ABSTRACT**

This article mainly introduces the work on SI fitting of encapsulated high-speed ABF materials and the simulation study on PI noise consistency. It focuses on how, during the material fitting process, the return loss SDD11 can be kept within an error of less than 1 dB, and how the PI noise error can be maintained within 5%.

#### **BIOGRAPHY**

Master's degree in Electromagnetic Field from University of Electronic Science and Technology of China.

Joined ZTE Microelectronics in 2021 as a Level 5 Technical Expert in the SIPI field, responsible for SIPI simulation technology and methodology for the

packaging team, and serves as the head of the Chengdu Packaging Department.

Previously worked at several well-known companies in the industry, offers basic SI simulation courses. Personal public account: <High-Speed Circuits and Signal Integrity>, @Half a RF Engineer

#### INDUSTRY PLENARY V

| TITLE   | Speed Up 112/224G Design with Clarity 3D Solver and Optimality Explorer |  |

|---------|-------------------------------------------------------------------------|--|

| TIME    | 16:20 – 16:50, November 5th                                             |  |

| VENUE   | HUALUXE Hall @Level 1(1 楼华邑宴会厅)                                         |  |

| SPEAKER | Kezhou Li                                                               |  |

#### ABSTRACT:

for 112/224Gbps SerDes.

As cloud applications and large language models like GPT become increasingly widespread, network providers are compelled to upgrade transmission bandwidth, which requires advanced SerDes technology. The OIF organization initiated the CEI-224G project in 2020; if the 112G SerDes PAM4 scheme is adopted, the fundamental frequency reaches 56GHz, posing significant challenges for high-speed signal transmission across entire systems. Conventional design and simulation workflows often optimize individual components, but robust SerDes development at 112/224Gbps demands entire channel path analysis and system-level design optimization, accounting for all components' interactions. This presentation introduces how Cadence Clarity 3D Solver and Optimality Explorer efficiently enable global design and optimization

#### **BIOGRAPHY**

Kezhou Li is a seasoned expert in electromagnetic simulation with over 15 years of experience. As a Director in Cadence's System Design and Analysis (SDA) Group, Kezhou leads the Product Engineering and Verification Team in China. He has witnessed Cadence's remarkable growth in the system simulation domain and plays a key role in shaping the roadmap for flagship tools in electronic simulation.

#### **INDUSTRY PLENARY VI**

| TITLE   | Evaluation and Solutions for Electrothermal and Mechanical Stress CHall |

|---------|-------------------------------------------------------------------------|

|         | enges in Large-Chip Applications                                        |

| TIME    | 16:50 – 17:20, November 5th                                             |

| VENUE   | HUALUXE Hall @Level 1(1 楼华邑宴会厅)                                         |

| SPEAKER | Yi Chen                                                                 |

#### **ABSTRACT**

With increasing chip size and power consumption, the electrical, thermal, and mechanical stress issues in chip applications are becoming deeply intertwined. This article introduces evaluation methods and corresponding solutions to address these electro-thermal-stress challenges.

#### **BIOGRAPHY**

Earned a Master's degree from Harbin Institute of Technology. Joined ZTE Corporation in 2007 and possesses 20 years of experience in hardware development. Currently serving as the principal leader of the SI/PI team for wireless digital hardware and server products, with focused expertise in SerDes/DDR high-speed interface

hardware design, evaluation, as well as SI/PI research related to chip packaging solutions and BBU/server architecture.

#### INDUSTRY PLENARY TALK I

| TITLE | Electromagnetic Compatibility (EMC) Simulation Applications in a Full- |  |

|-------|------------------------------------------------------------------------|--|

|       | Vehicle Environment.                                                   |  |

| TIME  | 8:40 – 9:10, November 6th                                              |  |

| VENUE | Liren Hall 2 @Level 1(1 楼里仁厅二)                                         |  |

**SPEAKER**

#### **ABSTRACT**

Ming Zhou

Electromagnetic Compatibility (EMC) Simulation Applications in a Full-Vehicle Environment. Abstract: Full-vehicle EMC simulation faces significant challenges, including numerous EMI noise sources, complex noise propagation paths, difficulties in model simplification, and the inability to easily create simulation models from within components. CST Studio Suite has a wealth of application cases in full-vehicle EMC simulation, covering simulations for Conducted Emissions (CE), Radiated Emissions (RE), and Bulk Current Injection (BCI).

#### **BIOGRAPHY**

Zhou Ming earned his Master of Engineering degree from Harbin Institute of Technology. He has long specialized in electromagnetic field simulation technology research and possesses rich engineering application experience, providing CST simulation guidance and technical support to major clients in the high-tech and automotive industries.

#### INDUSTRY PLENARY TALK II

| TITLE   | TBD                             |

|---------|---------------------------------|

| TIME    | 9:10 – 9:40, November 6th       |

| VENUE   | Liren Hall 2 @Level 1 (1 楼里仁厅二) |

| SPEAKER | TBD                             |

#### **ABSTRACT**

**TBD**

#### **BIOGRAPHY**

**TBD**

Technical Sessions - Thursday, NOVEMBER 6, 2025

| Room             | Technical Sessions – Thursday, NOVEMBER 6, 2025  HUALUXE Hall 1 HUALUXE Hall 3 Liren Hall 2                                                                                                                                                                                                                                         |                                                                                               |                                                                                                                                                                                                              |                                                   |                                                                                                                       |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| KOOIII           | SS1: Signal and Power Integrity for High-                                                                                                                                                                                                                                                                                           |                                                                                               |                                                                                                                                                                                                              |                                                   |                                                                                                                       |  |

|                  |                                                                                                                                                                                                                                                                                                                                     | onnect Design                                                                                 | SS3: Advance in Electromagnetism Simulation and Analysis Method                                                                                                                                              |                                                   | Industry Plenary Talk                                                                                                 |  |

| SESSION<br>CHAIR | Francesco de Paulis,<br>University of L'Aquila,<br>Italy                                                                                                                                                                                                                                                                            | Seungyoung Ahn,<br>Korea Advanced<br>Institute of Science<br>and Technology,<br>Korea (South) | Xiong Chen,<br>Xi'an Jiaotong<br>University, China                                                                                                                                                           | <b>Xiuqin Chu,</b><br>Xidian University,<br>China | <b>Ling Zhang,</b><br>Zhejiang University, China                                                                      |  |

| 08:40-<br>09:00  | LPDDR SIPI Design Experience in<br>Automotive Cockpit SoC and Microwave<br>Nondestructive Evaluation Technique for<br>Packaging Material ( <i>Invited</i> )<br>( <i>Chao Liu, Southeast University, China</i> )                                                                                                                     |                                                                                               | Exploring Advanced Packaging in 2.5D/3D IC EDA: A Unified Platform for Backend Physical Design Simulation and Verification ( <i>Invited</i> ) (Yi Zhao, Zhuhai Silicon Chip Technology Ltd., China)          |                                                   | Electromagnetic Compatibility (EMC) Simulation Applications in a Full-Vehicle Environment (Invited) (Ming ZHOU, CHINA |  |

| 09:00-<br>09:20  | Design and Analysis of Perforated Ground Plane for Mode Conversion Mitigation in High-Speed Differential Channel of Die-to- Die Interface (Hyunwoo Kim, Korea Advanced Institute of Science and Technology University, Korea (South))                                                                                               |                                                                                               | Fast EM Algorithms for Interconnects in 2.5D/3D Integrated Circuits ( <i>Invited</i> ) ( <i>Shunchuan Yang, Beihang University, China</i> )                                                                  |                                                   | SIMULIA Electromagnetics<br>Industry Process Senior<br>Consultant )                                                   |  |

| 09:20-<br>09:40  | Comparative Study of Delay Extraction Methods of Long SFP+ High Speed Cables for Signal Integrity Applications (John Xiao, Keysight, China & Keysight (China), China)  Physics-Constrained Differential Evolution for Continuous Decoupling Capacitor Placement and Orientation Optimization (Li Jiang, Zhejiang University, China) |                                                                                               | Industry Plenary Talk II                                                                                                                                                                                     |                                                   |                                                                                                                       |  |

| 09:40-<br>10:00  | Modeling Capacitive-Loaded Unintentional<br>Stubs in High-Speed Channels<br>(Nicolò Vicari, University of L'Aquila, Italy)                                                                                                                                                                                                          |                                                                                               | Dielectric Reconfigurable S-band Planar Phase Shifter (Yichen Liu, Xi'an Jiaotong University, China)                                                                                                         |                                                   |                                                                                                                       |  |

| 10:00-<br>10:20  | Random Jitter Amplification Coefficient<br>Calculation for NRZ PRBS Signal<br>(Tao Wei, Xidian University, China)                                                                                                                                                                                                                   |                                                                                               | Analysis of the Influence of Three - Proof Coating on the High - Speed Signal Transmission Performance of Embedded Computers (Zichun Zhang, Xi'an Aeronautics Computing Technique Research Institute, China) |                                                   | Panel Discussion                                                                                                      |  |

| 10:40-<br>11:00  | Comprehensive Measurement-to-Simulation Methodology for Better Gigabit Interconnect Evaluation and Exploration (Tim Wang Lee, Keysight Technologies, USA)                                                                                                                                                                           |                                                                                               | An Equation Based<br>Speed Differential<br>Fiber Wea<br>(Kai Li, Cisco Sys                                                                                                                                   | Pairs Affected by ave Effect                      |                                                                                                                       |  |

| 11:00-<br>11:20  | Design Challenges<br>Strategies for High-S<br>Fixt<br>(Lei Deng, LinkE Te                                                                                                                                                                                                                                                           | peed Connector Test<br>ures                                                                   | Addressing the Ev Growing Challenge High-Speed Intercon                                                                                                                                                      |                                                   | Panel Discussion I Addressing the Ever-                                                                               |  |

| 11:20-<br>11:40  | Propagation Under Re<br>Derived T                                                                                                                                                                                                                                                                                                   | Modeling of DFE Error sidual ISI Using SBR-Transitions In University, China)                  |                                                                                                                                                                                                              |                                                   | Growing Challenges in High-Speed Interconnect Designs in the AI Era: EDA Perspectives                                 |  |

| 11:40-<br>12:00  | Research on Phys<br>Automated Testing T<br>Standard Hard<br>(Chuangye Guo, Av<br>Computing Techniqu<br>Chi                                                                                                                                                                                                                          | Technology for Non-<br>lware Products<br>ic Xi'an Aeronautics<br>te Research Institute,       | Addressing the Radio Frequency Interference Problem Through Characteristic Mode Analysis (Xu Wang, Zhejiang University, China)                                                                               |                                                   |                                                                                                                       |  |

| Room             | HUALUXE Hall 1                                                                                                                                                                                                                                                                |                                                                                                                          | HUALUXE Hall 3                                                                                                                                 |                                                                                                                                      | Liren Hall 2                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|                  | SS2: Recent Advances in EMI/EMC                                                                                                                                                                                                                                               |                                                                                                                          | SS5: AI/ML based EMC/SI/PI Design                                                                                                              |                                                                                                                                      | Panel Discussion                                                              |

| SESSION<br>CHAIR | <b>Si-Ping Gao,</b><br>Nanjing University of<br>Aeronautics and<br>Astronautics, China                                                                                                                                                                                        | <b>Huapeng Zhao,</b> University of Electronic Science and Technology of China, China                                     | <b>Dawei Wang,</b><br>Hangzhou Dianzi<br>University, China                                                                                     | <b>Xiaohe Chen,</b><br>China University of<br>Petroleum, China                                                                       | <b>Bo Pu,</b><br>DeTooLIC Ltd.<br>Technology, China                           |

| 13:20-<br>13:40  | Recent Progress of Fast Direct Partial Element Equivalent Circuit Method ( <i>Invited</i> ) ( <i>Huapeng Zhao</i> , <i>University of Electronic Science</i> and Technology of China, China)                                                                                   |                                                                                                                          | Application of Optimization Algorithms in Channel Signal Integrity Design (Qihang Shang, DeTooLIC Ltd. Technology, China)                      |                                                                                                                                      | Panel Discussion II Data Center High-                                         |

| 13:40-<br>14:00  | Suppressing Evanescent Wave Coupling Using Anisotropic Metasurface in Small Cavity Circuit (Invited) (Da Yi, Chongqing University, China)                                                                                                                                     |                                                                                                                          | Multimodal Ma<br>(XiaoYang Wu, Hang Z<br>Chi                                                                                                   | High-Speed Link Surrogate Modeling Based on<br>Multimodal Machine Learning<br>(XiaoYang Wu, Hang Zhou Dian Zi University,<br>China)) |                                                                               |

| 14: 00-<br>14:20 | Recent Advances in YIG-Based Frequency Selective Limiters (Si-Ping Gao, Nanjing University of Aeronautics and Astronautics, China)  An Efficient Thermal-Aware Placement Method for Chiplet-Oriented Integrated Microsystems (Peng Zhang, Hangzhou Dianzi University, China)  |                                                                                                                          | Materials and Manufacturing                                                                                                                    |                                                                                                                                      |                                                                               |

| 14:20-<br>14:40  | A Reconfigurable Dual-Polarized Metasurface Capable of Switching Between Absorption and Transmission Modes (Pei Zhang, Zhejiang University, China)  Machine Learning-Assisted S-Parameter Frequency-Domain Extrapolation Method (Fei Zhou, Hangzhou Dianzi University, China) |                                                                                                                          | Panel Discussion III Data Center High-                                                                                                         |                                                                                                                                      |                                                                               |

| 14:40-<br>15:00  | Measurement of S                                                                                                                                                                                                                                                              | DNN-Based Prediction of Frequency- Dependent RLGC Parameters for Transmission Lines (Jiaqi He, Xidian University, China) |                                                                                                                                                | Speed Interconnect in<br>the AI Era: Part II -<br>Architecturing the<br>Interconnect for the                                         |                                                                               |

| 15:00-<br>15:20  | S-Band Tunable Impedance Matching Network with Varactor Diodes (Zhou Han, Xi'an Jiaotong University, China)                                                                                                                                                                   |                                                                                                                          | PCB Stack-Up Recognition Using LLMs (Jie Li, Southwest University of Science and Technology, China)                                            |                                                                                                                                      | Future                                                                        |

|                  | SS4: Power Integrity Design Techniques                                                                                                                                                                                                                                        |                                                                                                                          | SS6: Antenna Design Techniques                                                                                                                 |                                                                                                                                      |                                                                               |

| SESSION<br>CHAIR | <b>Jun Wang,</b><br>Xidian University, China                                                                                                                                                                                                                                  | <b>Xinglin Sun,</b><br>Zhejiang University,<br>China                                                                     | Guangxiao Luo,<br>North China Electric<br>Power University<br>(Baoding), China                                                                 | <b>Da Yi,</b> Chongqing University, China                                                                                            |                                                                               |

| 15:40-<br>16:00  | A Hierarchical Optin Framework for Broadb Circuit M (Yongjie Chen, Zhejia                                                                                                                                                                                                     | and MLCC Equivalent-                                                                                                     | Thermal Co-Simulation<br>Integrated Millimeter                                                                                                 | Mesh-Coupled Electro-<br>Method for Large-Scale<br>-Wave Phased Arrays<br>ai Laboratory, China)                                      | Panel Discussion IV Trends in Smart                                           |

| 16:00-<br>16:20  | Calculation Method for Statistical Distribution of Power Supply Noise in Chip-Package-PCB Co- Design (Yuhuan Luo, Xi'an University of Posts and Telecommunications, China)                                                                                                    |                                                                                                                          | Computational Modeling of a Microstrip<br>Antenna and Measurements with a Nano VNA<br>(Kenedy Marconi Geraldo Santos, IFBA, Brazil)            |                                                                                                                                      | Devices and Chall enges Related to Electromagnetic Interference in the AI Era |

| 16:20-<br>16:40  | Multi-Objective Decap Optimization Based on<br>Non-Dominated Sorting Genetic Algorithm<br>(Keyi Ding, Zhejiang University, China)                                                                                                                                             |                                                                                                                          | Radiolocati<br>(Marcelo B Peroto                                                                                                               |                                                                                                                                      | Era                                                                           |

| 16:40-<br>17:00  | Overestimation of Inductance in PDN Modeling:  A Study on MLCC Models  (Cailiang Fu, Southwest University of Science and Technology, China)                                                                                                                                   |                                                                                                                          | Dual Wideband Metasurface Based Linear to<br>Circular Polarizer for Transmission Mode<br>(Fatima Ghulam, Zhejiang Normal University,<br>China) |                                                                                                                                      |                                                                               |

| 17:00-<br>17:20  | Attention-Guided Reinforcement-Genetic Optimizer: Fast PDN Impedance Prediction and Decoupling Capacitor Design for Power Integrity (Qiyu Jiang, Beijing University of Posts and Telecommunications, China)                                                                   |                                                                                                                          | X-Band FSS for EMI (Saad Hassan Kiani                                                                                                          | Polarization-Insensitive<br>Shielding Applications<br>, Universiti Teknikal<br>aka, Malaysia)                                        |                                                                               |

| 17:20-<br>17:40  | Simulation and Test of 112Gbps SerDes Power<br>Noise<br>(Lingyun Liu, SANECHIPS Technology CO. LTD,<br>China)                                                                                                                                                                 |                                                                                                                          | Probe and Circuit<br>Recons<br>(Guangxiao Luo, North                                                                                           | Fransient Electric Field -Based Waveform truction h China Electric Power oding), China)                                              |                                                                               |

### Technical Sessions – Friday, NOVEMBER 7, 2025

| Rooms            | HUALUXE Hall 1                                                                                                                                                                                                                                                                                         | HUALUXE Hall 3                                                                                                                                             | Liren Hall 2 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                  | SS7: Electromagnetic Compatibility of<br>Integrated Circuits and Components                                                                                                                                                                                                                            | SS8: Advanced SI Modeling, Design, and Testing<br>Techniques                                                                                               | IBIS Summit  |

| SESSION<br>CHAIR | Fayu Wan, Nanjing University of Information Science and Technology, China  Anfeng Huang, DeTooLIC Ltd. Technology, China                                                                                                                                                                               | Lei Deng, LinkE Technologies, China  Si-Ping Gao, Nanjing University of Aeronautics and Astronautics, China                                                |              |

| 08:40-<br>09:00  | From Standard Interpretation to Testing Practice: Exploring the Path to High-Quality CDM Testing ( <i>Invited</i> ) ( <i>Bingsheng Gao, ESDEMC Technology LLC,</i> China)                                                                                                                              | A de-Embedding Method for High-Speed<br>Single-Ended Signals with Three-Port Test<br>Fixture<br>(Rui Miao, Xidian University, China)                       |              |

| 09:00-<br>09:20  | Research on the Influence of Signal Integrity of the Test Board on the CAN Transceivers Electromagnetic Interference Test (Qi Li, National New Energy Vehicles Technology Innovation Center & Automotive Chip Testing and Evaluation Key Laboratory State Administration for Market Regulation, China) | A Novel Method for Calculating Crosstalk de-<br>Embedding Transfer Function in High-Speed<br>Link<br>(Rui Chen, Xidian University, China)                  |              |

| 09:20-<br>9:40   | A Broadband Miniature TEM Cell for IC<br>EMC Measurement over 8 GHz<br>(Chenghao Lan, Jimei University, China)                                                                                                                                                                                         | Novel Methodology for Electrical Performance<br>Characterization of High-Speed Raw Cables<br>Under Thermal Stress<br>(Jimmy Hsu, Intel, Taiwan)            |              |

| 10:00-<br>10:20  | Comparative Study of BSS Algorithms for<br>Noise Source Localization<br>(Hailing Zhao, Southwest University of<br>Science and Technology, China)                                                                                                                                                       | Delay Matters: Enhancing S-Parameter Macromodeling Accuracy (Chenxi Liu, DeTooLIC Ltd. Technology, China)                                                  | IBIS Summit  |

| 10:20-<br>10:40  | Exploration of the Relationship Between<br>Copper Foil Microstructure and Etching<br>Behavior on PCB Signal Integrity<br>(Changdong Gu, Zhejiang Huanergy, China)                                                                                                                                      | Connectors for 400 Gbps-per-Lane Links: Challenges and Design Directions (Lei Deng, LinkE Technologies, China)                                             |              |

| 10:40-<br>11:00  | Charged Device Model Electrostatic Discharge Sensitivity Tester Based on 3D Vision (Minfeng Xia, Nanjing University of Information Science and Technology, China)                                                                                                                                      | Twinax Cables at 448 Gb/s: Challenges and Solutions (Lei Deng, LinkE Technologies, China)                                                                  |              |

| 11:00-<br>11:20  | Integrated Coaxial Resonator for Reconfigurable Passive Intermodulation Testing (Min Liang, Xi'an Jiaotong University, China)                                                                                                                                                                          | 2.4 GHz Wideband Tunable Impedance Matching Network (Bin Han, Xi'an Jiaotong University, China)                                                            |              |

| 11:20-<br>11:40  | Tunable Phase Shifter Using Monolithic Sliding Triple-Line Structure (Yuhan Liu, Xi'an Jiaotong University, China)                                                                                                                                                                                     | Implementation of an Adaptive DFE Algorithm (Wenbo Zhang, Avic Xi'an Aeronautics Computing Technique Research Institute', China)                           |              |

| 11:40-<br>12:00  | A Method for Generating Approximately<br>Non-Diffracting Möbius Rings<br>(Yueyi Yuan, Harbin Institute of Technology,<br>China)                                                                                                                                                                        | Research on GMSL Testing Technology in Multi-Physical Field Environments (Yuxu Huo, Avic Xi'an Aeronautics Computing Technique Research Institute', China) |              |

#### PANEL DISCUSSION I

| ТОРІС               | Addressing the Ever-Growing Challenges in High-Speed Interconnect Designs in the AI Era: EDA Perspectives                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIME                | 10:20 – 12:00, November 6th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VENUE               | Liren Hall 2 (里仁厅二)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PANEL CHAIR         | Bo Pu, TPC chair, International Workshop on Advanced Interconnects (WAI)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INVITED<br>PANELIST | Stanley Zheng, Director of External Cooperation Committee and Chief of Standards, EDA <sup>2</sup> Michael Liu, Senior product director, Empyrean Technology Haisan Wang, AE Director, Cadence Kefei Zhang, Technical Marketing Director, Semitronix Yin Sun, Vice President of Product Engineering, DeTooLIC Technology Ming Zhou, SIMULIA Electromagnetics Industry Process Senior Consultant, Dassault Systemes Haidong Zhang, Leading EM and Thermal Product Director, NineCube Xiuguo Jiang, EDA SE&CSM Manager, Keysight |

#### **KEY TOPICS INCLUDE:**

- Global and local Market Demands: EDA of high-speed and high bandwidth interconnects for Chiplet, data centers, AI systems, and supercomputing infrastructure.

- Innovative Solutions and Future Trends: Exploring cutting-edge solutions and technological advancements to meet the industry's demands.

We invite you to join this unique opportunity to connect with industry leaders and shape the future of EDA for high-speed and high bandwidth interconnect technologies.

#### BIO OF PANEL CHAIR

#### Bo Pu, TPC chair, International Workshop on Advanced Interconnects (WAI)

Dr. Bo Pu is the TPC chair of WAI. He was a Staff Engineer in charge of design methodology for AP, SerDes, HBM2/2E/3, DDR5 and GDDR6 from 14nm to 3nm as well as responsible for collaborating with Cadence and ANSYS in Samsung Semiconductor HQ, Korea. Then he joined Missouri University of Science and Technology, MO, USA as an assistant research professor. Currently He is the VP of DeTooLIC Technology. He published over 50 technical papers and holds 15 patents about high speed links and 2.5D/3D ICs.

He is the TPC chair and Member of the IEEE WAI, IEEE EMCS, IEEE APEMC, ISEMC and ACES. He was also awarded the 2014 URSI Young Scientists Award, 2022 APEMC Outstanding Young Scientists Award, and the 2020, 2021 Distinguish reviewer of IEEE Transactions on EMC, 2023 Outstanding Associate Editor of IEEE Access. Dr. Pu is a recipient of the Technical Achievement Award from IEEE EMC Society.

#### **BIOS OF INVITED PANELIST**